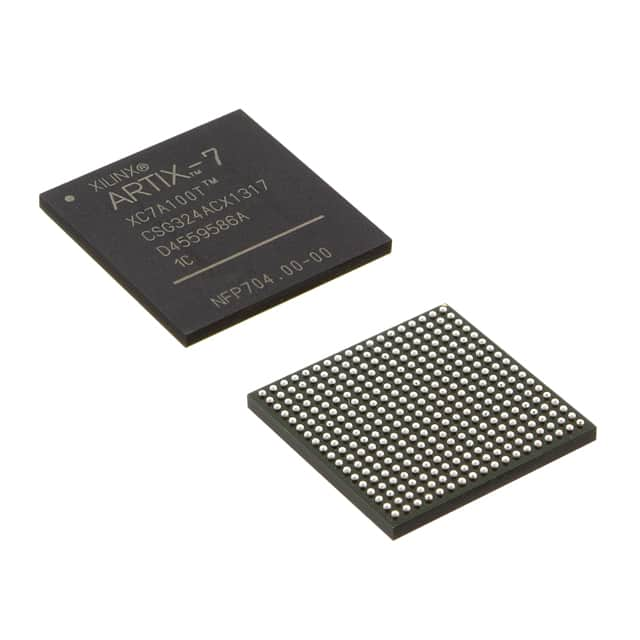

تراشه آی سی اصلی قابل برنامه ریزی XCVU440-2FLGA2892I IC FPGA 1456 I/O 2892FCBGA

ویژگی های محصول

| تایپ کنید | شرح |

| دسته بندی | مدارهای مجتمع (IC) |

| Mfr | AMD Xilinx |

| سلسله | Virtex® UltraScale™ |

|

| جعبه |

| استانداردپکیج d | 1 |

| وضعیت محصول | فعال |

| تعداد LAB/CLB | 316620 |

| تعداد عناصر/سلول های منطقی | 5540850 |

| مجموع بیت های RAM | 90726400 |

| تعداد ورودی/خروجی | 1456 |

| تامین کننده ولتاژ | 0.922 ~ 0.979 ولت |

| نوع نصب | نصب سطحی |

| دمای عملیاتی | -40 درجه سانتی گراد ~ 100 درجه سانتی گراد (TJ) |

| بسته / مورد | 2892-BBGA، FCBGA |

| بسته دستگاه تامین کننده | 2892-FCBGA (55×55) |

| شماره محصول پایه | XCVU440 |

استفاده از FPGA به عنوان پردازنده ترافیک برای امنیت شبکه

ترافیک به و از دستگاه های امنیتی (دیوار آتش) در سطوح مختلف رمزگذاری می شود و رمزگذاری/رمزگشایی L2 (MACSec) در گره های شبکه لایه پیوند (L2) (سوئیچ ها و روترها) پردازش می شود.پردازش فراتر از L2 (لایه MAC) معمولاً شامل تجزیه عمیق تر، رمزگشایی تونل L3 (IPSec) و ترافیک SSL رمزگذاری شده با ترافیک TCP/UDP است.پردازش بسته شامل تجزیه و طبقه بندی بسته های ورودی و پردازش حجم ترافیک بزرگ (1-20M) با توان عملیاتی بالا (25-400Gb/s) است.

با توجه به تعداد زیادی منابع محاسباتی (هسته) مورد نیاز، NPU ها را می توان برای پردازش بسته با سرعت نسبتاً بالاتر استفاده کرد، اما پردازش ترافیک مقیاس پذیر با تاخیر کم و با کارایی بالا امکان پذیر نیست زیرا ترافیک با استفاده از هسته های MIPS/RISC و زمان بندی چنین هسته هایی پردازش می شود. بر اساس در دسترس بودن آنها دشوار است.استفاده از وسایل امنیتی مبتنی بر FPGA می تواند به طور موثر این محدودیت های معماری مبتنی بر CPU و NPU را از بین ببرد.

پردازش امنیت در سطح برنامه در FPGA

FPGA ها برای پردازش امنیت درون خطی در فایروال های نسل بعدی ایده آل هستند زیرا آنها با موفقیت نیاز به عملکرد بالاتر، انعطاف پذیری و عملیات کم تاخیر را برآورده می کنند.علاوه بر این، FPGA ها همچنین می توانند توابع امنیتی در سطح برنامه را پیاده سازی کنند، که می تواند منابع محاسباتی را بیشتر ذخیره کند و عملکرد را بهبود بخشد.

نمونه های رایج پردازش امنیت برنامه در FPGA ها عبارتند از

- موتور تخلیه TTCP

- تطبیق عبارت منظم

- پردازش رمزگذاری نامتقارن (PKI).

- پردازش TLS

فناوری های امنیتی نسل بعدی با استفاده از FPGA

بسیاری از الگوریتمهای نامتقارن موجود در برابر کامپیوترهای کوانتومی آسیبپذیر هستند.الگوریتمهای امنیتی نامتقارن مانند RSA-2K، RSA-4K، ECC-256، DH و ECCDH بیشترین تأثیر را از تکنیکهای محاسبات کوانتومی دارند.پیاده سازی های جدید الگوریتم های نامتقارن و استانداردسازی NIST در حال بررسی هستند.

پیشنهادهای کنونی برای رمزگذاری پس کوانتومی شامل روش Ring-on-Error Learning (R-LWE) است.

- رمزنگاری کلید عمومی (PKC)

- امضای دیجیتال

- ایجاد کلید

اجرای پیشنهادی رمزنگاری کلید عمومی شامل عملیات ریاضی شناخته شده خاصی است (TRNG، نمونهگر نویز گاوسی، جمع چند جملهای، تقسیم کمیتساز چند جملهای باینری، ضرب و غیره).IP FPGA برای بسیاری از این الگوریتمها در دسترس است یا میتوان آن را با استفاده از بلوکهای ساختمانی FPGA، مانند موتورهای DSP و AI (AIE) در دستگاههای موجود و نسل بعدی Xilinx پیادهسازی کرد.

این مقاله سفید پیاده سازی امنیت L2-L7 را با استفاده از یک معماری قابل برنامه ریزی که می تواند برای تسریع امنیت در شبکه های لبه/دسترسی و فایروال های نسل بعدی (NGFW) در شبکه های سازمانی مستقر شود، توصیف می کند.